AMD Jaguar - garść szczegółów

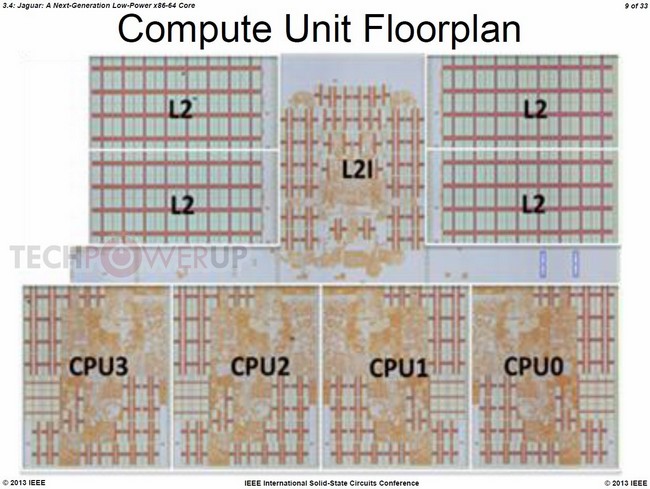

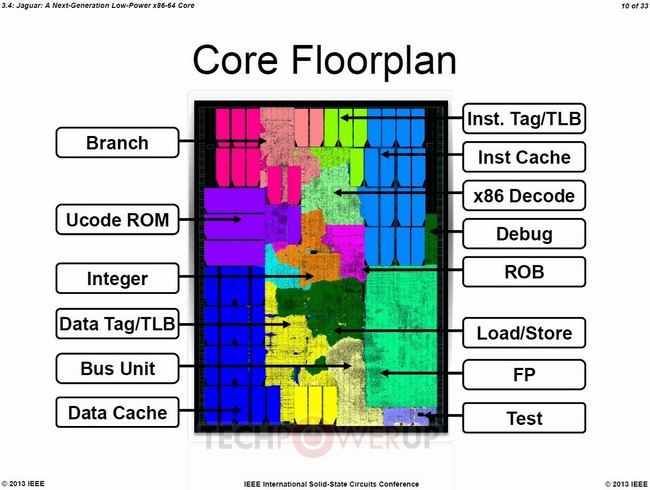

Firma AMD w czasie konferencji ISSC 2013 przedstawiła prezentację dotyczącą nowych procesorów opartych na rdzeniach Jaguar. Będą one zbudowane z jednostek CU, a każda z nich składa się z czterech rdzeni x86.

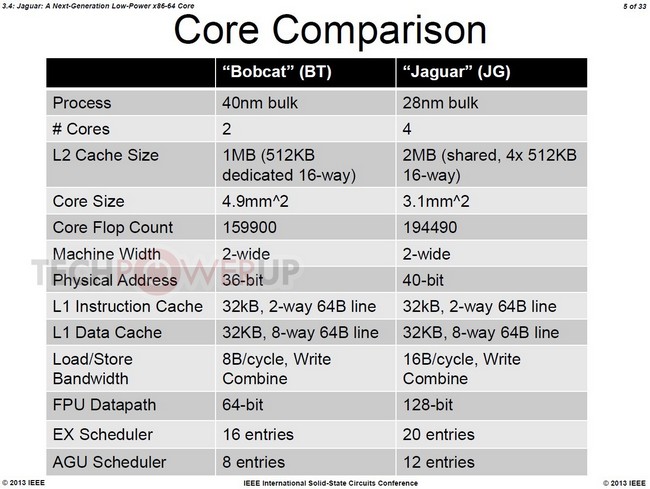

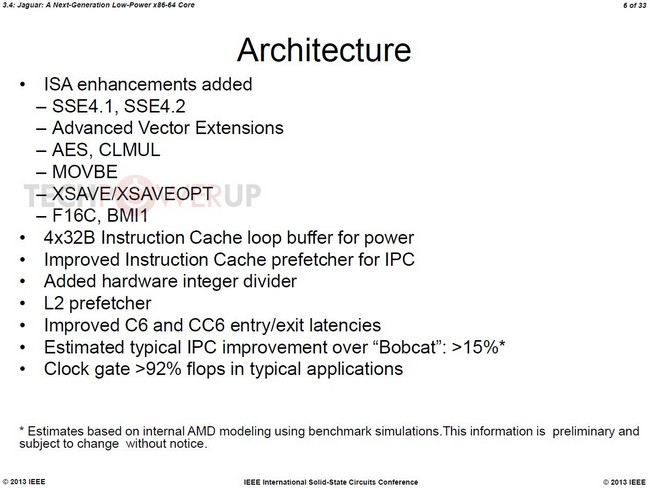

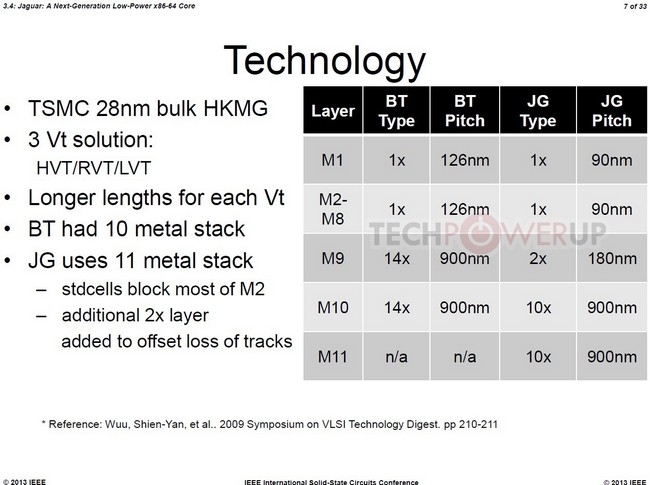

W odróżnieniu od architektury Bulldozer, tutaj mamy wszystkie rdzenie oddzielnie, które komunikują się za pomocą pamięci podręcznej L2 o pojemności 2 MB. Zastosowano tutaj 128-bitowe jednostki FPU, dodano nowy bufor pamięci do przechowywania instrukcji (jak w intelowskich Ivy Bridge i Sandy Bridge), zmieniono również budowę planisty. Mamy tutaj dostęp do następujących instrukcji: SSE 4.1 i SSE 4.2, AVX i AES, a także BMI, TBM, F16C, MOVBE i PCLMUL. Oprócz tego poszerzono szynę adresu do 40-bitów, co pozwoli zaadresować do 1 TB pamięci. Jaguary mają cechować się TDP na poziomie od 5 do 25 W.

AMD podaje, że nowe rozwiązania zapewnią minimum 15% wzrost wskaźnika IPC.

1836

1836 0

0 Poprzedni

Poprzedni

70

70

Komentarze